主な仕様

特性:

Package Code

DFN1616-6W

Number of terminal

8

Polarity

Pch

Drain-Source Voltage VDSS[V]

-30

Drain Current ID[A]

-3.1

RDS(on)[Ω] VGS=4V(Typ)

0.122

RDS(on)[Ω] VGS=4.5V(Typ)

0.108

RDS(on)[Ω] VGS=10V(Typ)

0.075

RDS(on)[Ω] VGS=Drive(Typ)

0.122

Total gate charge Qg[nC]

4.8

Power Dissipation (PD)[W]

1.5

Drive Voltage[V]

-4

Mounting Style

Surface mount

Storage Temperature (Min)[℃]

-55

Storage Temperature (Max)[℃]

150

Package Size [mm]

1.6x1.6 (t=0.8)

Common Standard

AEC-Q101 (Automotive Grade)

特長:

- 低オン抵抗

- 小型ハイパワーパッケージ

- 4V駆動

- 100%アバランシェ耐量試験

- 自動光学検査装置(AOI)対応 Wettable Flank電極部分 Min.130μm保証

製品概要

製品概要

近年、ADAS実現に必要不可欠な車載カメラは、設置スペースが限られていることから、搭載部品にも小型化の要求が高まっています。こうした市場要求に応えるため、大電流を保持したまま小型化が望める下面電極パッケージのMOSFETに注目が集まっています。

一方、車載部品においては、信頼性確保のため部品実装後に自動光学検査※1)が実施されていますが、下面電極パッケージには側面にメッキ加工がないため、車載で必要とされる半田高さ(130μm)を確保できず、実装後の半田づけ状態の確認が困難だという課題がありました。

ロームは、これまで超小型MOSFETをはじめ業界に先駆けた製品開発を行い、高い実績を誇ってきました。今回、独自工法を用いたWettable Flank形成技術※2)を導入したことにより、下面電極パッケージでも安定した半田フィレットの形成が可能になりました。業界で初めて※、パッケージ側面の電極部分の高さ130μmを保証しているため、部品実装後の外観検査で確実に半田づけ状態を確認できるようになります。

※2019年7月22日 ローム調べ

製品ラインアップ

| 品名 | 極性 [ch] |

ドレイン ・ソース 間耐圧 VDSS[V] |

ドレイン 電流 ID[A] |

駆動電圧 [V] |

ドレイン・ソース間オン抵抗 | |||||||||||

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

| RDS(on)[mΩ] @VGS=10V |

RDS(on)[mΩ] @VGS=4.5V |

RDS(on)[mΩ] @VGS=4.0V |

RDS(on)[mΩ] @VGS=2.5V |

RDS(on)[mΩ] @VGS=1.8V |

RDS(on)[mΩ] @VGS=1.5V |

|||||||||||

| Typ. | Max. | Typ. | Max. | Typ. | Max. | Typ. | Max. | Typ. | Max. | Typ. | Max. | |||||

RV4E031RP HZG |

P | 30 | 3.1 | 4.0 | 75 | 105 | 108 | 152 | 122 | 172 | ─ | ─ | ─ | ─ | ─ | ─ |

RV4C020ZP HZG |

P | 20 | 2.0 | 2.5 | ─ | ─ | 180 | 260 | ─ | ─ | 240 | 340 | 320 | 450 | 400 | 560 |

特長

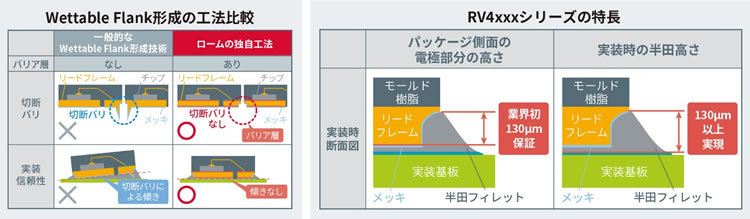

1.独自工法を用いたWettable Flank形成技術により、パッケージ側面の電極部分の高さ130μm(min.)を保証

Wettable Flank形成技術では、パッケージ側面のリードフレーム部に切り込みを入れてメッキ加工を行います。しかし、リードフレームに切り込みを入れる際に発生するバリは、切り込みの高さが高くなればなるほど多く発生します。

そこで、ロームはバリを抑制するためにリードフレーム全面にバリア層を設ける独自工法を開発。これにより部品実装時の製品の傾きや半田不良を防ぐことができ、DFN1616パッケージ品(1.6mm×1.6mm)としては、業界で初めて、パッケージ側面の電極部分の高さ130μm(min.)保証を実現しました。

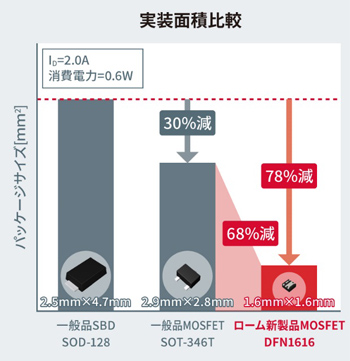

2.小型の下面電極 MOSFETへの置き換えで実装面積を削減

例えば、電流2.0A、消費電力0.6Wの場合、車載市場で多く使われている端子付きパッケージMOSFETでは、SBDと比べて30%実装面積を小さくできます。一方、下面電極パッケージのMOEFETは、下面が電極となっているので放熱性が良く、小型でありながら大電流化を実現できます。これにより従来の一般品SBDと比べて78%、一般品MOSFETと比べて68%実装面積を削減することができます。

用語説明

*1)外観検査

自動光学検査やAOI(Automated Optical Inspection)とも呼ぶ。たとえば、実装基板をカメラでスキャンし、部品の欠落や品質の欠陥、半田付け状態などを検査する。

*2)Wettable Flank技術

QFNやDFNなどの下面電極パッケージの側面のリードフレーム部に切り込みを入れてメッキ加工を施し、側面にも電極を形成する技術のこと。